Publications

2026

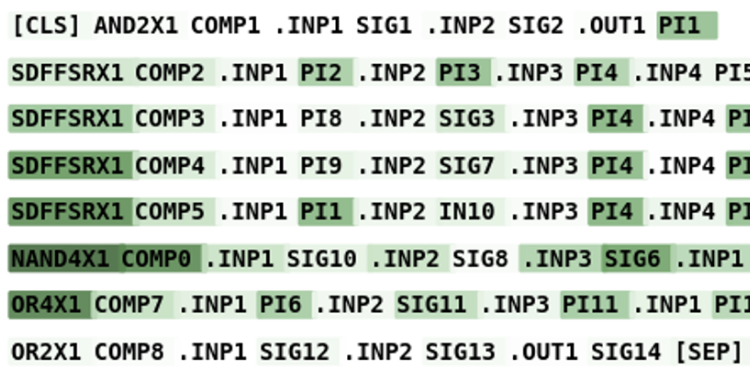

ReBERT: LLM for Gate-Level to Word-Level Reverse Engineering, in Generative AI for Next Generation Computer Design

Springer Nature

·

06 Jun 2026

·

[no id info]

Feature-Aware Trojan Alteration to Evade ML-Based Detection

IEEE VLSI Test Symposium (VTS)

·

27 Apr 2026

·

[no id info]

BERT-HIT: A Transformer-Based Approach for Hardware Trojan Detection in Gate-Level Netlists

IEEE International Symposium on Quality Electronic Design (ISQED)

·

08 Apr 2026

·

[no id info]

2025

CADI: Carbon-Aware Distributed Inference

2025 IEEE International Conference on Omni-layer Intelligent Systems (COINS)

·

04 Aug 2025

·

doi:10.1109/COINS65080.2025.11125725

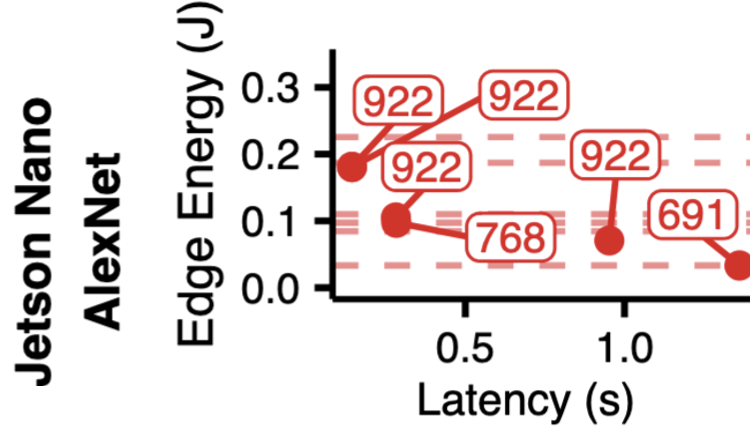

FreDDI: Frequency-Driven DNN Partitioning in Distributed Inference

2025 IEEE International Conference on Smart Computing (SMARTCOMP)

·

16 Jun 2025

·

doi:10.1109/SMARTCOMP65954.2025.00106

ReBERT: LLM for Gate-Level to Word-Level Reverse Engineering

2025 Design, Automation & Test in Europe Conference (DATE)

·

31 Mar 2025

·

doi:10.23919/DATE64628.2025.10993097

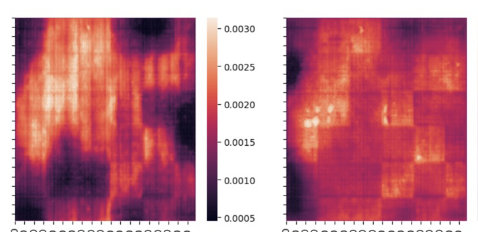

Static IR Drop Prediction with Limited Data from Real Designs

Proceedings of the 30th Asia and South Pacific Design Automation Conference

·

20 Jan 2025

·

doi:10.1145/3658617.3697592

2024

Efficient and Effective Neural Networks for Automatic Test Pattern Generation

Proceedings of the 2024 ACM/IEEE International Symposium on Machine Learning for CAD

·

09 Sep 2024

·

doi:10.1145/3670474.3685939

Static IR Drop Prediction with Attention U-Net and Saliency-Based Explainability

arXiv

·

06 Aug 2024

·

doi:arXiv:2408.03292v1

DIME: Distributed Inference Model Estimation for Minimizing Profiled Latency

2024 IEEE International Conference on Smart Computing (SMARTCOMP)

·

29 Jun 2024

·

doi:10.1109/SMARTCOMP61445.2024.00081

A Systematic Framework for Opportunistic Pruning of Deep Neural Networks on Edge Devices

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

06 Jun 2024

·

[no id info]

On Neural Networks for Automatic Test Pattern Generation

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

06 Jun 2024

·

[no id info]

DNNP: An Automated, Hybrid Framework for Neural Network Pruning on Edge Devices

Poster at 7th Annual Conference on Machine Learning and Systems (MLSys)

·

13 May 2024

·

[no id info]

2023

Neural Network Partitioning for Fast Distributed Inference

2023 24th International Symposium on Quality Electronic Design (ISQED)

·

05 Apr 2023

·

doi:10.1109/ISQED57927.2023.10129343

ObfusX: Routing obfuscation with explanatory analysis of a machine learning attack

Integration

·

01 Mar 2023

·

doi:10.1016/j.vlsi.2022.10.013

Block Pruning for Enhanced Efficiency in Convolutional Neural Networks

arXiv

·

01 Jan 2023

·

doi:10.48550/arXiv.2312.16904

2022

CAP’NN: A Class-aware Framework for Personalized Neural Network Inference

ACM Transactions on Embedded Computing Systems

·

30 Sep 2022

·

doi:10.1145/3520126

$\text{Edge}^{n}$ AI: Distributed Inference with Local Edge Devices and Minimal Latency

2022 27th Asia and South Pacific Design Automation Conference (ASP-DAC)

·

17 Jan 2022

·

doi:10.1109/ASP-DAC52403.2022.9712496

2021

Sampling-Based Approximate Logic Synthesis: An Explainable Machine Learning Approach

2021 IEEE/ACM International Conference On Computer Aided Design (ICCAD)

·

01 Nov 2021

·

doi:10.1109/ICCAD51958.2021.9643484

AirNN: A Featherweight Framework for Dynamic Input-Dependent Approximation of CNNs

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Oct 2021

·

doi:10.1109/TCAD.2020.3033750

A Mixture of Experts Approach for Low-Cost DNN Customization

IEEE Design & Test

·

01 Aug 2021

·

doi:10.1109/MDAT.2020.2977065

Lorax: Machine Learning-Based Oracle Reconstruction With Minimal I/O Patterns

2021 IEEE Computer Society Annual Symposium on VLSI (ISVLSI)

·

01 Jul 2021

·

doi:10.1109/ISVLSI51109.2021.00033

Logic Synthesis Meets Machine Learning: Trading Exactness for Generalization

2021 Design, Automation & Test in Europe Conference & Exhibition (DATE)

·

01 Feb 2021

·

doi:10.23919/DATE51398.2021.9473972

ObfusX

Proceedings of the 26th Asia and South Pacific Design Automation Conference

·

18 Jan 2021

·

doi:10.1145/3394885.3431600

2020

CHaPR: Efficient Inference of CNNs via Channel Pruning

2020 International Conference on Omni-layer Intelligent Systems (COINS)

·

01 Aug 2020

·

doi:10.1109/COINS49042.2020.9191636

CAP’NN: Class-Aware Personalized Neural Network Inference

2020 57th ACM/IEEE Design Automation Conference (DAC)

·

01 Jul 2020

·

doi:10.1109/DAC18072.2020.9218741

Explainable DRC Hotspot Prediction with Random Forest and SHAP Tree Explainer

2020 Design, Automation & Test in Europe Conference & Exhibition (DATE)

·

01 Mar 2020

·

doi:10.23919/DATE48585.2020.9116488

Logic Synthesis Meets Machine Learning: Trading Exactness for Generalization

arXiv

·

01 Jan 2020

·

doi:10.48550/arXiv.2012.02530

2019

Analysis of Security of Split Manufacturing Using Machine Learning

IEEE Transactions on Very Large Scale Integration (VLSI) Systems

·

01 Dec 2019

·

doi:10.1109/TVLSI.2019.2929710

Power-efficient ReRAM-aware CNN model generation

Integration

·

01 Nov 2019

·

doi:10.1016/J.VLSI.2019.08.003

Dynamic Reconfiguration of CNNs for Input-Dependent Approximation

20th International Symposium on Quality Electronic Design (ISQED)

·

01 Mar 2019

·

doi:10.1109/ISQED.2019.8697843

Efficient Inference of CNNs via Channel Pruning

arXiv

·

01 Jan 2019

·

doi:10.48550/arXiv.1908.03266

2018

Exploring Energy and Accuracy Tradeoff in Structure Simplification of Trained Deep Neural Networks

IEEE Journal on Emerging and Selected Topics in Circuits and Systems

·

01 Dec 2018

·

doi:10.1109/JETCAS.2018.2833383

Power-Efficient ReRAM-Aware CNN Model Generation

2018 IEEE 36th International Conference on Computer Design (ICCD)

·

01 Oct 2018

·

doi:10.1109/ICCD.2018.00033

Hybrid Signal Selection

Post-Silicon Validation and Debug

·

02 Sep 2018

·

doi:10.1007/978-3-319-98116-1_5

Analysis of security of split manufacturing using machine learning

Proceedings of the 55th Annual Design Automation Conference

·

24 Jun 2018

·

doi:10.1145/3195970.3195991

A Comparative Study of Local Net Modeling Using Machine Learning

Proceedings of the 2018 Great Lakes Symposium on VLSI

·

30 May 2018

·

doi:10.1145/3194554.3194579

Design Rule Violation Hotspot Prediction Based on Neural Network Ensembles

arXiv

·

01 Jan 2018

·

doi:10.48550/arXiv.1811.04151

A Mixture of Expert Approach for Low-Cost Customization of Deep Neural Networks

arXiv

·

01 Jan 2018

·

doi:10.48550/arXiv.1811.00056

Exploring energy and accuracy tradeoff in structure simplification of trained deep neural networks

2018 23rd Asia and South Pacific Design Automation Conference (ASP-DAC)

·

01 Jan 2018

·

doi:10.1109/ASPDAC.2018.8297345

2017

Are Proximity Attacks a Threat to the Security of Split Manufacturing of Integrated Circuits?

IEEE Transactions on Very Large Scale Integration (VLSI) Systems

·

01 Dec 2017

·

doi:10.1109/TVLSI.2017.2748018

Golden-Free Trojan Detection

The Hardware Trojan War

·

30 Nov 2017

·

doi:10.1007/978-3-319-68511-3_9

Dynamic Planning of Local Congestion From Varying-Size Vias for Global Routing Layer Assignment

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Aug 2017

·

doi:10.1109/TCAD.2017.2695889

TraPL

Proceedings of the 54th Annual Design Automation Conference 2017

·

18 Jun 2017

·

doi:10.1145/3061639.3062335

Technology Mapping with All Spin Logic

IEEE/ACM Design, Automation & Test In Europe Conference & Exhibition (DATE)

·

27 Mar 2017

·

[no id info]

Improving Detailed Routability and Pin Access with 3D Monolithic Standard Cells

Proceedings of the 2017 ACM on International Symposium on Physical Design

·

19 Mar 2017

·

doi:10.1145/3036669.3036676

Technology mapping with all spin logic

Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017

·

01 Mar 2017

·

doi:10.23919/DATE.2017.7927123

Flexible interconnect in 2.5D ICs to minimize the interposer's metal layers

2017 22nd Asia and South Pacific Design Automation Conference (ASP-DAC)

·

01 Jan 2017

·

doi:10.1109/ASPDAC.2017.7858351

2016

Are proximity attacks a threat to the security of split manufacturing of integrated circuits?

Proceedings of the 35th International Conference on Computer-Aided Design

·

07 Nov 2016

·

doi:10.1145/2966986.2967006

A procedure for improving the distribution of congestion in global routing

IEEE/ACM Design, Automation & Test In Europe Conference & Exhibition (DATE)

·

14 Mar 2016

·

[no id info]

Dynamic planning of local congestion from varying-size vias for global routing layer assignment

2016 21st Asia and South Pacific Design Automation Conference (ASP-DAC)

·

01 Jan 2016

·

doi:10.1109/ASPDAC.2016.7428040

2015

On using control signals for word-level identification in a gate-level netlist

Proceedings of the 52nd Annual Design Automation Conference

·

07 Jun 2015

·

doi:10.1145/2744769.2744878

Online and Operand-Aware Detection of Failures Utilizing False Alarm Vectors

Proceedings of the 25th edition on Great Lakes Symposium on VLSI

·

20 May 2015

·

doi:10.1145/2742060.2742097

Automatic die placement and flexible I/O assignment in 2.5D IC design

Sixteenth International Symposium on Quality Electronic Design

·

01 Mar 2015

·

doi:10.1109/ISQED.2015.7085480

2014

A Hybrid Approach for Fast and Accurate Trace Signal Selection for Post-Silicon Debug

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Jul 2014

·

doi:10.1109/TCAD.2014.2307533

Multi-mode trace signal selection for post-silicon debug

2014 19th Asia and South Pacific Design Automation Conference (ASP-DAC)

·

01 Jan 2014

·

doi:10.1109/ASPDAC.2014.6742963

2013

A Sensor-Assisted Self-Authentication Framework for Hardware Trojan Detection

IEEE Design & Test

·

01 Oct 2013

·

doi:10.1109/MDAT.2013.2255913

A fast and scalable multidimensional multiple-choice knapsack heuristic

ACM Transactions on Design Automation of Electronic Systems

·

01 Oct 2013

·

doi:10.1145/2541012.2541014

Power-Driven Global Routing for Multisupply Voltage Domains

VLSI Design

·

02 Jul 2013

·

doi:10.1155/2013/905493

Collaborative Multiobjective Global Routing

IEEE Transactions on Very Large Scale Integration (VLSI) Systems

·

01 Jul 2013

·

doi:10.1109/TVLSI.2012.2205717

Online and operand-aware detection of failures by utilizing false alarm vectors

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

01 Jun 2013

·

[no id info]

Planning for local net congestion in global routing

Proceedings of the 2013 ACM International symposium on Physical Design

·

24 Mar 2013

·

doi:10.1145/2451916.2451940

A hybrid approach for fast and accurate trace signal selection for post-silicon debug

IEEE/ACM Design, Automation & Test In Europe Conference & Exhibition (DATE)

·

23 Mar 2013

·

[no id info]

A Hybrid Approach for Fast and Accurate Trace Signal Selection for Post-Silicon Debug

Design, Automation & Test in Europe Conference & Exhibition (DATE), 2013

·

01 Jan 2013

·

doi:10.7873/DATE.2013.111

2012

A hybrid approach for fast and accurate trace signal selection for post-silicon debug

IEEE International Workshop on Microprocessor Test and Verification (MTV)

·

01 Dec 2012

·

[no id info]

Post-Silicon Failing-Path Isolation Incorporating the Effects of Process Variations

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Jul 2012

·

doi:10.1109/TCAD.2012.2187206

Confidentiality preserving integer programming for global routing

Proceedings of the 49th Annual Design Automation Conference

·

03 Jun 2012

·

doi:10.1145/2228360.2228487

Custom on-chip sensors for post-silicon failing path isolation in the presence of process variations

2012 Design, Automation & Test in Europe Conference & Exhibition (DATE)

·

01 Mar 2012

·

doi:10.1109/DATE.2012.6176726

A sensor-assisted self-authentication framework for hardware trojan detection

2012 Design, Automation & Test in Europe Conference & Exhibition (DATE)

·

01 Mar 2012

·

doi:10.1109/DATE.2012.6176698

2011

Congestion analysis for global routing via integer programming

2011 IEEE/ACM International Conference on Computer-Aided Design (ICCAD)

·

01 Nov 2011

·

doi:10.1109/ICCAD.2011.6105337

Power-driven global routing for MSV domains

IEEE/ACM Design, Automation & Test In Europe Conference & Exhibition (DATE)

·

14 Mar 2011

·

[no id info]

GRIP: Global Routing via Integer Programming

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Jan 2011

·

doi:10.1109/TCAD.2010.2066030

Bound-Based Statistically-Critical Path Extraction Under Process Variations

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Jan 2011

·

doi:10.1109/TCAD.2010.2072670

2010

Automation tools for post-silicon debug of timing errors

IEEE International Workshop on Microprocessor Test and Verification (MTV)

·

01 Dec 2010

·

[no id info]

A pareto-algebraic framework for signal power optimization in global routing

Proceedings of the 16th ACM/IEEE international symposium on Low power electronics and design

·

18 Aug 2010

·

doi:10.1145/1840845.1840935

Representative path selection for post-silicon timing prediction under variability

Proceedings of the 47th Design Automation Conference

·

13 Jun 2010

·

doi:10.1145/1837274.1837371

Post-silicon diagnosis of segments of failing speedpaths due to manufacturing variations

Proceedings of the 47th Design Automation Conference

·

13 Jun 2010

·

doi:10.1145/1837274.1837344

A parallel integer programming approach to global routing

Proceedings of the 47th Design Automation Conference

·

13 Jun 2010

·

doi:10.1145/1837274.1837323

Representative path selection for post-silicon timing prediction under variability

ACM Workshop on Timing Issues in the Specification of Digital Systems (TAU)

·

01 Apr 2010

·

[no id info]

Runtime temperature-based power estimation for optimizing throughput of thermal-constrained multi-core processors

2010 15th Asia and South Pacific Design Automation Conference (ASP-DAC)

·

01 Jan 2010

·

doi:10.1109/ASPDAC.2010.5419815

2009

PaRS: Parallel and Near-Optimal Grid-Based Cell Sizing for Library-Based Design

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Nov 2009

·

doi:10.1109/TCAD.2009.2028682

Statistical static timing analysis considering leakage variability in power gated designs

Proceedings of the 2009 ACM/IEEE international symposium on Low power electronics and design

·

19 Aug 2009

·

doi:10.1145/1594233.1594247

GRIP

Proceedings of the 46th Annual Design Automation Conference

·

26 Jul 2009

·

doi:10.1145/1629911.1629999

Adjustment-Based Modeling for Timing Analysis Under Variability

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Jul 2009

·

doi:10.1109/TCAD.2009.2018874

False Path Aware Timing Yield Estimation under Variability

2009 27th IEEE VLSI Test Symposium

·

01 May 2009

·

doi:10.1109/VTS.2009.17

Bound-based identification of timing-violating paths under variability

2009 Asia and South Pacific Design Automation Conference

·

01 Jan 2009

·

doi:10.1109/ASPDAC.2009.4796493

2008

PaRS: Fast and near-optimal grid-based cell sizing for library-based design

2008 IEEE/ACM International Conference on Computer-Aided Design

·

01 Nov 2008

·

doi:10.1109/ICCAD.2008.4681559

Adjustment-based modeling for Statistical Static Timing Analysis with high dimension of variability

2008 IEEE/ACM International Conference on Computer-Aided Design

·

01 Nov 2008

·

doi:10.1109/ICCAD.2008.4681571

SynECO: Incremental technology mapping with constrained placement and fast detail routing for predictable timing improvement

2008 IEEE International Conference on Computer Design

·

01 Oct 2008

·

doi:10.1109/ICCD.2008.4751915

A parallel and randomized algorithm for large-scale discrete dual-Vt assignment and continuous gate sizing

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

01 Jun 2008

·

[no id info]

SynECO: Technology remapping with incremental constrained placement and exact timing estimation

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

01 Jun 2008

·

[no id info]

A Dual-Vt low leakage SRAM array robust to process variations

2008 IEEE International Symposium on Circuits and Systems (ISCAS)

·

01 May 2008

·

doi:10.1109/ISCAS.2008.4541484

Fast and accurate statistical static timing analysis with skewed process parameter variation

IET Circuits, Devices & Systems

·

10 Apr 2008

·

doi:10.1049/iet-cds:20070189

Fast and Accurate Statistical Static Timing Analysis with Skewed Process Parameter Variation

9th International Symposium on Quality Electronic Design (isqed 2008)

·

01 Mar 2008

·

doi:10.1109/ISQED.2008.4479825

Robust Estimation of Timing Yield with Partial Statistical Information on Process Variations

9th International Symposium on Quality Electronic Design (isqed 2008)

·

01 Mar 2008

·

doi:10.1109/ISQED.2008.4479718

A parallel and randomized algorithm for large-scale discrete dual-Vt assignment and continuous gate sizing

Proceeding of the thirteenth international symposium on Low power electronics and design - ISLPED '08

·

01 Jan 2008

·

doi:10.1145/1393921.1393937

2007

Statistical timing analysis using Kernel smoothing

2007 25th International Conference on Computer Design

·

01 Oct 2007

·

doi:10.1109/ICCD.2007.4601886

A dual-Vt assignment algorithm of SRAM array considering process-induced Vt variations

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

01 Jun 2007

·

[no id info]

Comparison of Dual-Vt Configurations of SRAM Cell Considering Process-Induced Vt Variations

2007 IEEE International Symposium on Circuits and Systems

·

01 May 2007

·

doi:10.1109/ISCAS.2007.377982

Variability Driven Joint Leakage-Delay Optimization Through Gate Sizing with Provabale Convergence

20th International Conference on VLSI Design held jointly with 6th International Conference on Embedded Systems (VLSID'07)

·

01 Jan 2007

·

doi:10.1109/VLSID.2007.176

2006

Probabilistic Evaluation of Solutions in Variability-Driven Optimization

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Dec 2006

·

doi:10.1109/TCAD.2006.882529

A statistical methodology for wire-length prediction

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

·

01 Jul 2006

·

doi:10.1109/TCAD.2005.855885

Variability driven gate sizing for binning yield optimization

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

01 Jun 2006

·

[no id info]

Probabilistic evaluation of solutions in variability-driven optimization

Proceedings of the 2006 international symposium on Physical design

·

09 Apr 2006

·

doi:10.1145/1123008.1123013

Effective techniques for the generalized low-power binding problem

ACM Transactions on Design Automation of Electronic Systems

·

01 Jan 2006

·

doi:10.1145/1124713.1124718

FPGA Dynamic Power Minimization through Placement and Routing Constraints

EURASIP Journal on Embedded Systems

·

01 Jan 2006

·

doi:10.1155/ES/2006/31605

Variability driven gate sizing for binning yield optimization

Proceedings of the 43rd annual conference on Design automation - DAC '06

·

01 Jan 2006

·

doi:10.1145/1146909.1147152

2005

Variability-driven buffer insertion considering correlations

2005 International Conference on Computer Design

·

02 Oct 2005

·

doi:10.1109/ICCD.2005.114

Power-driven simultaneous resource binding and floorplanning: a probabilistic approach

IEEE Transactions on Very Large Scale Integration (VLSI) Systems

·

01 Aug 2005

·

doi:10.1109/TVLSI.2005.853618

Variability driven buffer insertion considering correlations

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

01 Jun 2005

·

[no id info]

Efficient stochastic pruning for variability-driven dual-Vth leakage optimization

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

01 Jun 2005

·

[no id info]

Voltage scheduling under unpredictabilities: a risk management paradigm

ACM Transactions on Design Automation of Electronic Systems

·

01 Apr 2005

·

doi:10.1145/1059876.1059884

Wake-up protocols for controlling current surges in MTCMOS-based technology

Proceedings of the ASP-DAC 2005. Asia and South Pacific Design Automation Conference, 2005.

·

21 Jan 2005

·

doi:10.1109/ASPDAC.2005.1466478

Simultaneous floorplanning and resource binding

Proceedings of the 2005 conference on Asia South Pacific design automation - ASP-DAC '05

·

01 Jan 2005

·

doi:10.1145/1120725.1120952

Probabilistic dual-Vth leakage optimization under variability

Proceedings of the 2005 international symposium on Low power electronics and design - ISLPED '05

·

01 Jan 2005

·

doi:10.1145/1077603.1077641

2004

Efficient statistical timing analysis through error budgeting

IEEE/ACM International Conference on Computer Aided Design, 2004. ICCAD-2004.

·

11 Oct 2004

·

doi:10.1109/ICCAD.2004.1382623

Wire-length prediction using statistical techniques

IEEE/ACM International Conference on Computer Aided Design, 2004. ICCAD-2004.

·

11 Oct 2004

·

doi:10.1109/ICCAD.2004.1382666

Variability inspired implementation selection problem

IEEE/ACM International Conference on Computer Aided Design, 2004. ICCAD-2004.

·

11 Oct 2004

·

doi:10.1109/ICCAD.2004.1382612

Empirical models for net-length probability distribution and applications

IEEE Transactions on Very Large Scale Integration (VLSI) Systems

·

01 Oct 2004

·

doi:10.1109/TVLSI.2004.834235

Simultaneous floorplanning and binding: A probabilistic approach

IEEE/ACM International Workshop on Logic & Synthesis (IWLS)

·

01 Jun 2004

·

[no id info]

High level techniques for power-grid noise immunity

Proceedings of the 14th ACM Great Lakes symposium on VLSI

·

26 Apr 2004

·

doi:10.1145/988952.988957

2003

Effective graph theoretic techniques for the generalized low power binding problem [IC high level synthesis]

Proceedings of the 2003 International Symposium on Low Power Electronics and Design, 2003. ISLPED '03.

·

27 Aug 2003

·

doi:10.1109/LPE.2003.1231852

A probabilistic approach to buffer insertion

ICCAD-2003. International Conference on Computer Aided Design (IEEE Cat. No.03CH37486)

·

01 Jan 2003

·

doi:10.1109/ICCAD.2003.159738

Simultaneous Vt selection and assignment for leakage optimization

Proceedings of the 2003 international symposium on Low power electronics and design - ISLPED '03

·

01 Jan 2003

·

doi:10.1109/LPE.2003.1231851