Projects

Our research interests span machine learning for better chip design, design automation for better machine learning including in distributed settings with edge devices, all aspects of IC-CAD including high-level design and layout synthesis, and hardware security. In recent years, we have been using explainable machine learning to improve computer-aided design for Integrated Circuits. Browse our current and past research projects.

The projects may be searched by the tags below.

Current Projects

The goal of this project is to utilize Explainable Artificial Intelligence (XAI) to take the use of AI within the chip design process to the next level by allowing AI-based explainability to guide optimization.

Past Projects

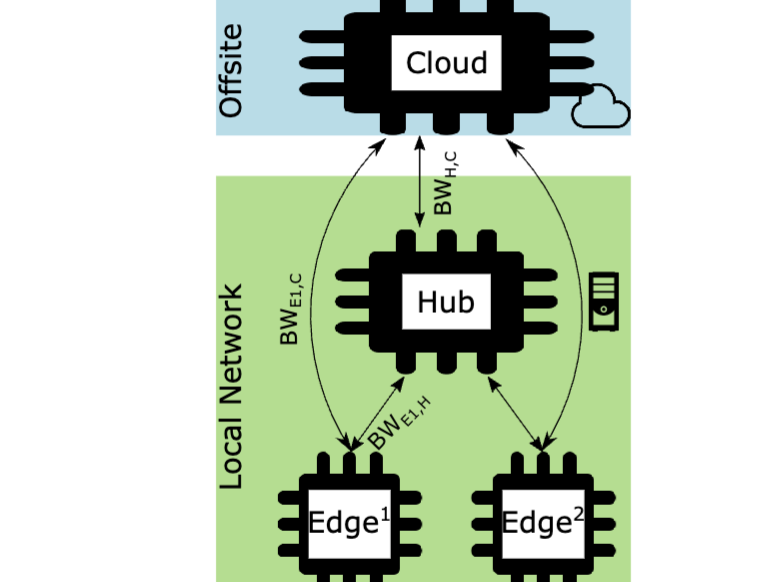

In this project, new techniques are investigated to directly deploy Deep Neural Networks onto networked devices, to perform inference with consideration for latency and energy consumption.

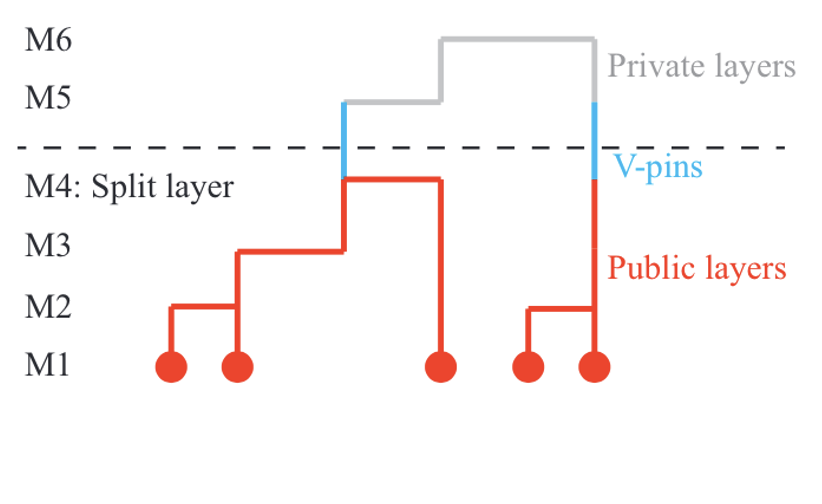

This project is on studying the security of chip fabrication by an untrusted foundry. The fabrication technique, known as split manufacturing, is based on partial sharing of the chip design information with the untrusted foundry.

This project aims to develop CAD tools that incorporate major design rules within a key, higher stage of the design flow, namely the global routing stage with the aim to bridge the gap with the lower detailed routing stage.

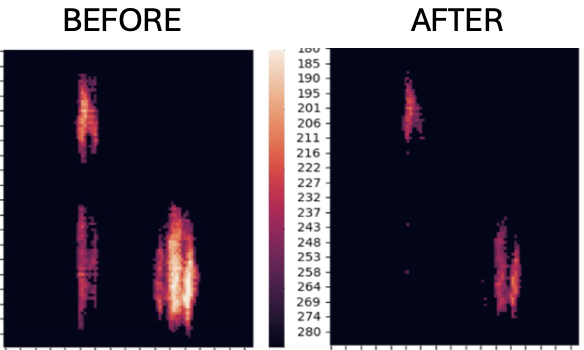

Timing errors are malfunctions causing setup and hold time violations. This research aims to automate debug of timing errors by relying on few on-chip measurements to learn about the rest of the chip.

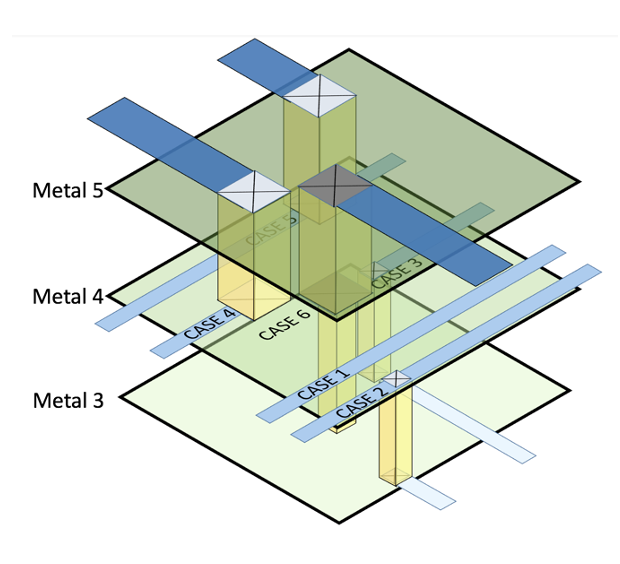

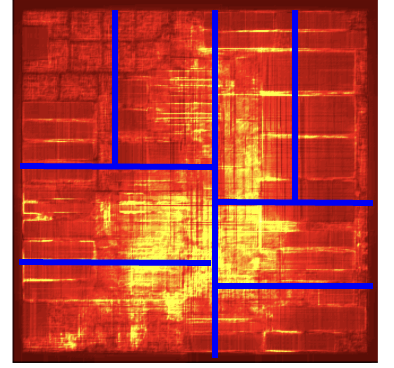

In modern IC designs, several new factors contribute to routing congestion including significantly different wire size and spacing among the metal layers, sizes of inter-layer vias, local congestion due to pin density and wiring inside a global-cell. This research aims to develop techniques for fast congestion analysis at global routing to increase correlation with detailed routing.

With the aid of large-scale parallelism provided by computational grids, the research aims to demonstrate that the use of a computational technique called integer programming, which was previously viewed as too time-consuming for global routing, can help generate significantly higher quality solutions while meeting practical runtime requirements.

In modern IC design, smaller components are less tolerant to manufacturing-induced variations; their performance may turn out so poor that the IC may have to be entirely redesigned in order to meet the performance specs. This research aims to develop a framework for producing IC designs that are robust with respect to imperfections.

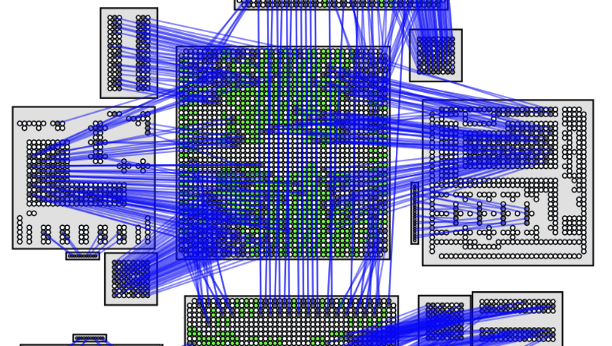

This project provides a framework for design automation of 2.5D interposer-based multi-die ICs. Our approach is designed for (but not limited to) 2.5D ICs that contain one or more dies with flexible I/Os—such as FPGA dies.

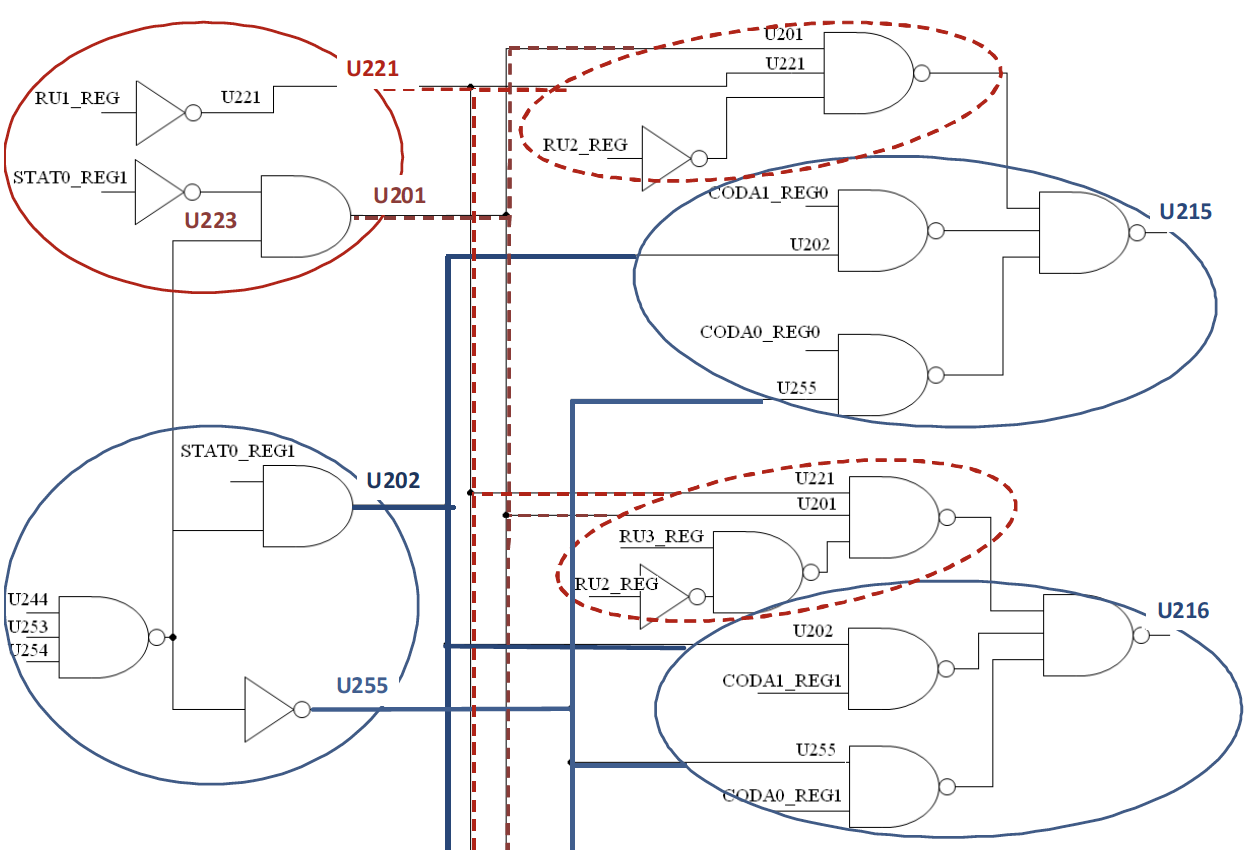

This project investigates the impact of control signals to aid in partial structural matching. Structural matching is used in netlist reverse engineering to identify groups of bits belonging to the same word.